ABMJB-903

### Moisture Sensitivity Level: MSL=1

#### FEATURES:

- Low power and miniature package programmable jitter attenuator

- Input frequency up to 200MHz

- Output frequency up to 840MHz

- Jitter attenuation 20dB at 3 MHz spur frequency

- Additive phase jitter or phase jitter floor:

- 55fs for 1.875MHz to 20MHz

- 251fs for 12MHz to 20MHz

- Single ended CMOS input

- One differential or two single ended outputs. Output logic types supported are LVPECL, LVDS, HCSL and LVCMOS (single ended or differential).

- Operating temperature range from -40°C to +85°C

- 24-pin QFN RoHS-complaint package

- Related devices:

- ABMJB-902: LVCMOS, period jitter cleaning.

## > APPLICATIONS:

- 1/10/40/100 Gigabiy Ethernet (GbE)

- SONET/SDH

- PCI-Express

- CPRI/OBSAI wireless base stations

- Fibre Channel

- SAS/SATA

- DIMM

### STANDARD SPECIFICATIONS:

**Absolute Maximum Ratings** (1)

| Parameters                                           | Min. | Тур. | Max.                 | Units | Notes          |

|------------------------------------------------------|------|------|----------------------|-------|----------------|

| Supply Voltage (V <sub>DD</sub> , V <sub>DDO</sub> ) |      |      | +4.6                 | V     |                |

| Input Voltage (V <sub>IN</sub> )                     | -0.5 |      | V <sub>DD</sub> +0.5 | V     |                |

| Lead Temperature                                     |      |      | +260                 | °C    | Soldering, 20s |

| Case Temperature                                     |      |      | +115                 | °C    |                |

| Storage Temperature (T <sub>S</sub> )                | -65  |      | +150                 | °C    |                |

Operation Ratings (2)

| Parameters                                                   | Min.   | Typ. | Max.   | Units | Notes     |

|--------------------------------------------------------------|--------|------|--------|-------|-----------|

| Supply Voltage (V <sub>DD</sub> , V <sub>DDO</sub> )         | +2.375 |      | +3.465 | V     |           |

| Junction Thermal Resistance ( <sub>JA</sub> ) <sup>(3)</sup> |        |      | 50     | °C/W  | Still-Air |

| Ambient Temperature (T <sub>A</sub> )                        | -40    |      | +85    | °C    |           |

### DC Electrical Characteristics (4)

$V_{DD} = V_{DDO} = 3.3V \pm 5\%$  or  $2.5V \pm 5\%$ ;  $T_A = -40$ °C to +85°C

| Parameters                                          | Min.   | Тур. | Max.   | Units | Notes                                                              |

|-----------------------------------------------------|--------|------|--------|-------|--------------------------------------------------------------------|

| Power Supply Voltage (V <sub>DD</sub> )             | +2.375 |      | +3.465 | V     |                                                                    |

|                                                     |        | 100  | 120    | mA    | LVPECL, 321.5MHz, Outputs open                                     |

| Total Supply Current, $V_{DD} + V_{DDO}$ $(I_{DD})$ |        | 80   | 100    | mA    | HCSL (PCIe), 100MHz, Outputs terminated with 50 to V <sub>SS</sub> |

|                                                     |        | 70   | 90     | mA    | 2 x LVCMOS, 125MHz, Outputs open                                   |

## LVCMOS Inputs (OE, REFIN) DC Electrical Characteristics (4)

$V_{DD} = V_{DDO} = 3.3V \pm 5\%$  or  $2.5V \pm 5\%$ :  $T_A = -40^{\circ}$ C to  $+85^{\circ}$ C

| Parameters                            | Min.          | Тур. | Max.                 | Units | Notes                          |

|---------------------------------------|---------------|------|----------------------|-------|--------------------------------|

| Input High Voltage (V <sub>IH</sub> ) | $70\% V_{DD}$ |      | V <sub>DD</sub> +0.3 | V     |                                |

| Input Low Voltage (V <sub>IN</sub> )  | $V_{SS}$ -0.3 |      | $30\%~V_{DD}$        | V     |                                |

| Input High Current (I <sub>IH</sub> ) |               |      | 150                  | μA    | $V_{DD} = V_{IN} = 3.465V$     |

| Input Low Current (I <sub>IL</sub> )  | -150          |      |                      | μA    | $V_{DD} = 3.465V, V_{IN} = 0V$ |

ABMJB-903

### LVDS Output DC Electrical Characteristics (4)

$V_{DD} = V_{DDO} = 3.3V \pm 5\%$  or  $2.5V \pm 5\%$ ;  $T_A = -40$ °C to +85°C;  $R_L = 100\Omega$  across Q and /Q

| Parameters                                    | Min. | Тур. | Max. | Units | Notes       |

|-----------------------------------------------|------|------|------|-------|-------------|

| Differential Output Voltage (VoD)             | 275  | 350  | 475  | mV    | See page 10 |

| $V_{OD}$ Magnitude Change ( $\Delta V_{OD}$ ) |      |      | 40   | mV    |             |

| Offset Voltage (Vos)                          | 1.15 | 1.25 | 1.5  | V     |             |

| $V_{OD}$ Magnitude Change ( $\Delta V_{OS}$ ) |      |      | 50   | mV    |             |

## **HCSL Output DC Electrical Characteristics** (4)

$V_{DD} = V_{DDO} = 3.3V \pm 5\%$  or  $2.5V \pm 5\%$ ;  $T_A = -40$ °C to +85°C;  $R_L = 50\Omega$  to  $V_{SS}$

| Parameters                                 | Min. | Typ. | Max. | Units | Notes           |

|--------------------------------------------|------|------|------|-------|-----------------|

| Output High Voltage (V <sub>OH</sub> )     | 660  | 700  | 850  | mV    | See page 8 & 10 |

| Output Low Voltage (V <sub>OL</sub> )      | -150 | 0    | 27   | mV    | See page 8 & 10 |

| Output Voltage Swing (V <sub>SWING</sub> ) | 630  | 700  | 1000 | mV    | See page 8 & 10 |

### LVPECL Output DC Electrical Characteristics (4)

$V_{DD} = V_{DDO} = 3.3V \pm 5\%$  or 2.5V \pm 5%;  $T_A = -40$ °C to +85°C;  $R_L = 50\Omega$  to  $V_{DD} - 2V$

| Parameters                                 | Min.                   | Тур.           | Max.            | Units | Notes          |

|--------------------------------------------|------------------------|----------------|-----------------|-------|----------------|

| Output High Voltage (V <sub>OH</sub> )     | V <sub>DD</sub> -1.145 | $V_{DD}$ -0.97 | $V_{DD}$ -0.845 | V     | See page 8 & 9 |

| Output Low Voltage (V <sub>OL</sub> )      | V <sub>DD</sub> -1.945 | $V_{DD}$ -1.77 | $V_{DD}$ -1.645 | V     | See page 8 & 9 |

| Output Voltage Swing (V <sub>SWING</sub> ) | 0.6                    | 0.8            | 1.0             | V     | See page 8 & 9 |

## LVCMOS Output DC Electrical Characteristics (4)

$V_{DD} = V_{DDO} = 3.3V \pm 5\%$  or 2.5V \pm 5\%;  $T_A = -40$ °C to +85°C;  $R_L = 50\Omega$  to  $V_{DD}/2$

| Parameters                             | Min.              | Тур. | Max. | Units | Notes           |

|----------------------------------------|-------------------|------|------|-------|-----------------|

| Output High Voltage (V <sub>OH</sub> ) | $V_{\rm DD}$ -0.7 |      |      | V     | See page 8 & 10 |

| Output Low Voltage (V <sub>OL</sub> )  |                   |      | 0.6  | V     |                 |

ABMJB-903

## **LVPECL AC Electrical Characteristics** (4, 5, 6, 10)

$V_{DD} = V_{DDO} = 3.3V \pm 5\%$  or  $2.5V \pm 5\%$ ;  $T_A = -40$ °C to +85°C, unless otherwise noted

| Parameters                                     | Min. | Typ. | Max. | Units | Notes                                 |

|------------------------------------------------|------|------|------|-------|---------------------------------------|

| Output Frequency (F <sub>OUT</sub> )           | 12   |      | 840  | MHz   |                                       |

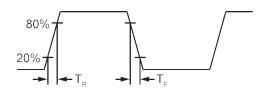

| LVPECL Output Rise/Fall Time $(T_R/T_F)$       | 80   | 175  | 350  | ps    | 20% - 80%                             |

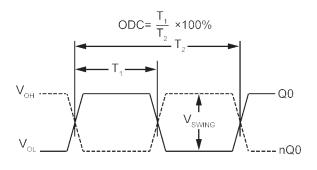

| Ontrod Patra Coals (ODC)                       | 48   | 50   | 52   | %     | $F_{OUT}$ < 350MHz                    |

| Output Duty Cycle (ODC)                        | 45   | 50   | 55   | 70    | $F_{OUT} \ge 350MHz$                  |

| PLL Lock Time (T <sub>LOCK</sub> )             |      |      | 20   | ms    |                                       |

| RMS Phase Jitter @ 156.25MHz                   |      | 251  |      | fs    | Integration range (12kHz to 20MHz)    |

| with Clean Input Signal $(T_{jit}(\emptyset))$ |      | 55   |      | fs    | Integration range (1.875MHz to 20MHz) |

## **LVDS AC Electrical Characteristics** (4, 5, 6, 7)

$V_{DD} = V_{DDO} = 3.3V \pm 5\%$  or  $2.5V \pm 5\%$ ;  $T_A = -40$ °C to +85°C, unless otherwise noted

| Parameters                                          | Min. | Typ. | Max. | Units | Notes                                 |

|-----------------------------------------------------|------|------|------|-------|---------------------------------------|

| Output Frequency (F <sub>OUT</sub> )                | 12   |      | 840  | MHz   |                                       |

| LVDS Output Rise/Fall Time $(T_R/T_F)$              | 100  | 160  | 400  | ps    | 20% - 80%                             |

| Output Duty Cycle (ODC)                             | 48   | 50   | 52   | %     | < 350MHz                              |

| Output Duty Cycle (ODC)                             | 45   | 50   | 55   | 70    | ≥350MHz                               |

| PLL Lock Time (T <sub>LOCK</sub> )                  |      |      | 20   | ms    |                                       |

| RMS Phase Jitter @ 156.25MHz $(T_{jit}(\emptyset))$ |      | 60   |      | fs    | Integration range (1.875MHz to 20MHz) |

## HCSL AC Electrical Characteristics (4, 5, 6, 8)

$V_{DD} = V_{DDO} = 3.3V \pm 5\%$  or  $2.5V \pm 5\%$ ;  $T_A = -40$ °C to +85°C, unless otherwise noted

| Parameters                                       | Min. | Typ. | Max. | Units | Notes                              |

|--------------------------------------------------|------|------|------|-------|------------------------------------|

| Output Frequency (F <sub>OUT</sub> )             | 12   |      | 840  | MHz   |                                    |

| LVDS Output Rise/Fall Time $(T_R/T_F)$           | 150  | 300  | 450  | ps    | 20% - 80%                          |

|                                                  | 48   | 50   | 52   | %     | < 350MHz                           |

| Output Duty Cycle (ODC)                          | 45   | 50   | 55   | 70    | ≥350MHz                            |

| PLL Lock Time (T <sub>LOCK</sub> )               |      |      | 20   | ms    |                                    |

| RMS Phase Jitter @ 100MHz $(T_{jit}(\emptyset))$ |      | 250  |      | fs    | Integration range (12kHz to 20MHz) |

ABMJB-903

## **LVCMOS AC Electrical Characteristics** (4, 5, 6, 9)

$V_{DD} = V_{DDO} = 3.3V \pm 5\%$  or  $2.5V \pm 5\%$ ;  $T_A = -40$ °C to +85°C, unless otherwise noted

| Parameters                                              | Min.          | Typ. | Max.           | Units    | Notes                                 |

|---------------------------------------------------------|---------------|------|----------------|----------|---------------------------------------|

| Output Frequency (F <sub>OUT</sub> )                    | 12            |      | 250            | MHz      |                                       |

| REFIN Frequency (F <sub>REF</sub> )                     | 12            |      | 200            | MHz      |                                       |

| REFIN Amplitude (V <sub>REF</sub> )                     | $40\%~V_{DD}$ |      | $V_{DD} + 0.6$ | $V_{PP}$ |                                       |

| Output Rise/Fall Time (T <sub>R</sub> /T <sub>F</sub> ) | 100           |      | 500            | ps       | 20% - 80%                             |

| Output Duty Cycle (ODC)                                 | 45            | 50   | 55             |          |                                       |

| PLL Lock Time (T <sub>LOCK</sub> )                      |               |      | 20             | ms       |                                       |

| RMS Phase Jitter @ 125MHz $(T_{jit}(\emptyset))$        |               | 55   |                | fs       | Integration range (1.875MHz to 20MHz) |

#### Notes:

- 1. Exceeding the absolute maximum ratings may damage the device.

- 2. The device is not guaranteed to function outside tis operating ratings.

- 3. Package thermal resistance assumes the exposed pad is soldered (or equivalent) to the device's most negative potential on the PCB.

- 4. The circuit is designed to meet the AC and DC specifications shown in the Electrical Characteristics tables after thermal equilibrium has been established.

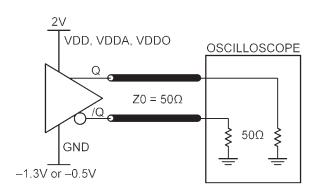

- 5. See Section 7.1.7 through 7.1.10 for load test circuit examples.

- 6. All phase noise measurements were taken with an Agilent 5052B phase noise system.

- 7. Outputs terminated  $100\Omega$  between Q and /Q. All unused outputs must be terminated.

- 8. Output load is  $50\Omega$  to  $V_{SS}$ .

- 9. Output load is  $50\Omega$  to  $V_{DD}/2$ .

- 10. Output load is  $50\Omega$  to  $V_{DD}$ -2V.

#### **OPTIONS AND PART IDENTIFICATION:**

Please refer to the <u>ABMJB-903 Part Number and Configuration Guide</u> for available part numbers and configurations.

ABMJB-903

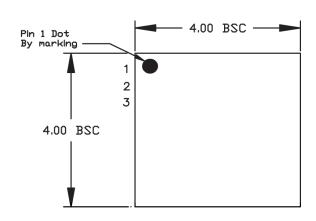

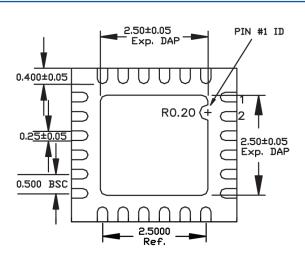

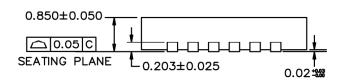

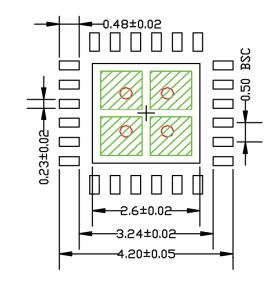

#### **OUTLINE DIMENSION:**

TOP VIEW

BOTTOM VIEW

SIDE VIEW

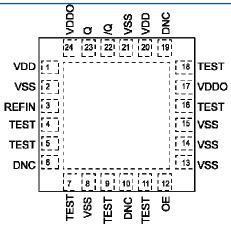

| Pin No.                   | Configuration |

|---------------------------|---------------|

| 22                        | Q             |

| 23                        | /Q            |

| 3                         | REFIN         |

| 12                        | OE            |

| 1, 20                     | VDD           |

| 17, 24                    | VDDO          |

| 2, 8, 13, 14,<br>15, 21   | VSS           |

| 4, 5, 7, 9,<br>11, 16, 18 | DNC           |

| 6, 10, 19                 | DNC           |

| ePad                      | Exposed Pad   |

RECOMMENDED LAND PATTERN

#### Notes:

- 1. Max package warpage is 0.05mm.

- 2. Max allowable burr is 0.076mm in all directions.

- 3. Pin 1 is on top and will be laser marked.

- 4. Red circles in land pattern indicate thermal vias. Size should be 0.30 0.35M in diameter and should be connected to GND for max thermal performance.

- 5. Green rectangles (shaded area) indicate solder stencil opening on exposed pad area. Size should be 1.00 x 1.00 mm in size, 1.20mm pitch.

**Dimension: mm**

ABMJB-903

#### **PIN DESCRIPTION:**

24-Pin QFN package

| 24-Fin QFN package        |             |          |           |                                                                                                                     |  |

|---------------------------|-------------|----------|-----------|---------------------------------------------------------------------------------------------------------------------|--|

| Pin No.                   | Pin Name    | Pin Type | Pin Level | Function                                                                                                            |  |

| 22                        | Q           |          |           | Clock output                                                                                                        |  |

| 23                        | /Q          | О        | Various   | Can be programmed to one of the following logic types: (1) LVPECL, LVDS, HCSL or LVCMOS                             |  |

| 3                         | REFIN       | I, (SE)  | Various   | Reference clock input Can be programmed to either LVCMOS levels or smaller amplitude signals from other logic types |  |

| 12                        | OE          | I        | LVCMOS    | Output enable control input with pull-up (45k )                                                                     |  |

| 1, 20                     | VDD         | PWR      |           | Core power supply                                                                                                   |  |

| 17, 24                    | VDDO        | PWR      |           | Output buffer power supply                                                                                          |  |

| 2, 8, 13, 14,<br>15, 21   | VSS         | PWR      |           | Power supply ground                                                                                                 |  |

| 4, 5, 7, 9,<br>11, 16, 18 | DNC         |          |           | Used for production test Do not connect anything to these pins                                                      |  |

| 6, 10, 19                 | DNC         |          |           | Not internally connected. No need to connect anything to these pins.                                                |  |

| ePad                      | Exposed Pad | GND      |           | The center pad must be connected to the ground plane both for electrical ground and thermal relief.                 |  |

#### Notes:

1. In case of LVCMOS, the output pair can provide two single-ended LVCMOS outputs.

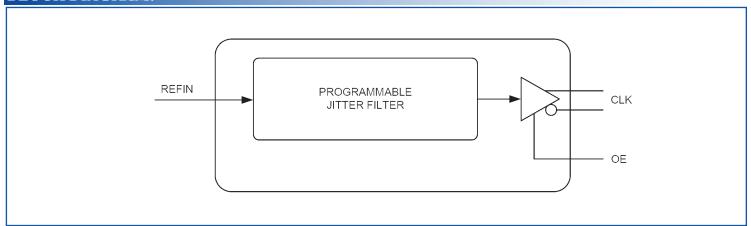

#### **BLOCK DIAGRAM:**

ABMJB-903

#### **FUNCTIONAL DESCRIPTION**

ABMJB-903 series is a very flexible, advanced programmable jitter filter design for high performance, small form-factor applications. The ABMJB-903 accepts a reference clock input between 12MHz and 200MHz and is capable of producing one differential output up to 840MHz or two single ended outputs up to 250MHz. The most common configuration will be with the same input and output frequency but this flexible design also allows frequency translation from one frequency to another frequency, as long as both frequencies are within the specified ranges for input and output.

#### **Jitter Attenuation**

Typically the jitter attenuation settings will be optimized for one particular input and output frequency. Customization of attenuation properties is possible.

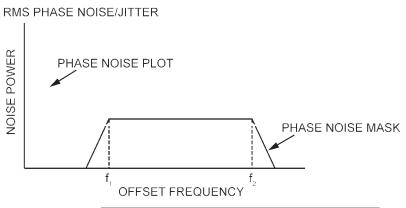

The lowest possible output phase jitter, or phase jitter floor, is 251fs for the 12kHz to 20MHz integration range and 55fs for the Gigabit Ethernet integration range of 1.875MHz to 20MHz. The ABMLB-903 excels at attenuating deterministic jitter that presents itself as spurs in the phase noise plot above 1MHz.

#### **Clock Output**

The output pins Q and /Q make a differential output that can be programmed to several different logic types: LVPECL, LVDS, HCSL or LVCMOS. In the case of LVCMOS, there are three possible configurations:

- 1. One single-ended output with the complementary pin disabled to a high impedance.

- 2. Two single-ended, in-phase outputs.

- 3. A differential output with opposite phases at the two output pins

#### **Output Frequency**

The most common configuration is where the output frequency is the same as the input frequency. However, frequency translations are possible. The input frequency upper limit is 200MHz, but the output can go up to 840MHz.

#### **Output Enable (OE)**

The Output Enable feature allows the user to enable and disable the clock output(s) by toggling the OE pin. The OE pin incorporates a  $45k\Omega$  pull-up resistor giving a default condition of logic "1" that enables the output(s).

#### Reference (Noisy) Clock Input (REFIN)

The input requires a single-ended CMOS signal. The frequency range for the input is 12MHz to 200MHz.

ABMJB-903

#### **APPLICATION INFORMATION**

#### **Power Supply Filtering Recommendations**

Preferred filter, using Micrel's MIC94300 or MIC94310 Ripple Blocker<sup>TM</sup>:

Alternative, traditional filter, using a ferrite bead:

VDD PLANE

$$0.5\Omega$$

$10\mu\text{F}$

$0.047\mu\text{F}$

$0.01\mu\text{F}$

$4.7\text{nF}$

### **Power Supply Decoupling**

Place the smallest value decoupling capacitor (4.7nF above) between the VDD and VSS pins, as close as possible to those pins and at the same side of the PCB as the IC. The shorter the physical path from VDD to capacitor and back from capacitor to VSS, the more effective the decoupling. Use one 4.7nF capacitor for each VDD pin on the ABMJB-903.

The impedance value of the ferrite bead (FB) needs to be between 240 and 600 with a saturation current ≥150mA.

VDDO pins connect directly to the VDD plane. All VDD pins on the ABMJB-903 connect to VDD after the power supply filter.

#### **Output Traces**

Design the traces for the output signals according to the output logic requirements. If LVCMOS is unterminated, add a 30 resistor in series with the output, as close as possible to the output pin, and start a 50 trace on the other side of the resistor.

For differential traces, you can either use a differential design or two separate 50 traces. For EMI reasons, it is better to use a differential design.

LVDS can be AC-coupled or DC-coupled to its termination.

#### **Duty Cycle Timing**

ABMJB-903

#### > APPLICATION INFORMATION

#### All Outputs Rise/Fall Time

#### **RMS Phase Noise Jitter**

RMS JITTER = VAREA UNDER THE MASKED PHASE NOISE PLOT

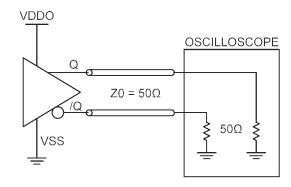

#### **LVPECL Output Load and Test Circuit**

ABMJB-903

#### **APPLICATION INFORMATION**

#### **HCSL Output Load and Test Circuit**

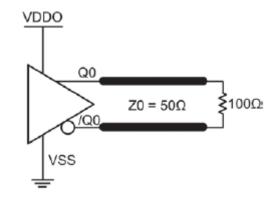

#### **LVDS Output Load and Test Circuit**

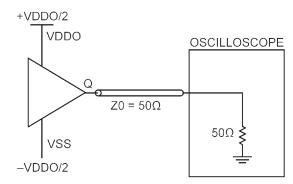

#### **LVCMOS Output Load and Test Circuit**

ABMJB-903

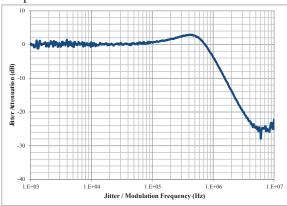

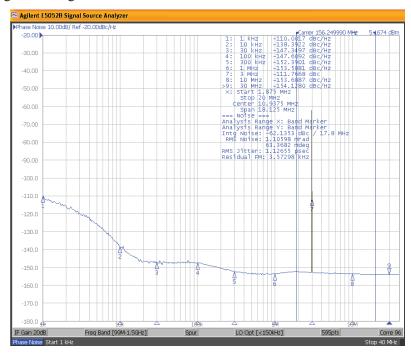

### > JITTER ATTENUATION PERFORMANCE

The jitter attenuating frequency response was measured at 156.25MHz.

The jitter attenuation works like a low-pass filter for frequency modulated signals or noise. The bandwidth for this low pass filter is 500kHz with a 12dB/octave slope above 500kHz. At about 6MHz the noise floor of this measurement is reached but in reality, the attenuation continues with the 12dB/octave slope.

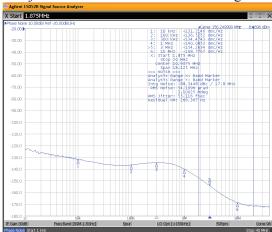

Phase noise performance with a clean input clock:

156.25MHz with 55fs<sub>RMS</sub> for phase jitter for 1.875MHz to 20MHz integration range

156.25MHz with 251fs<sub>RMS</sub> for phase jitter for 12kHz to 20MHz integration range

ABMJB-903

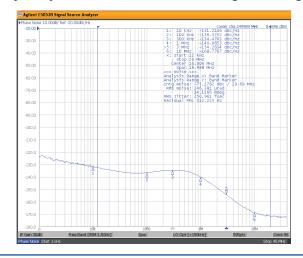

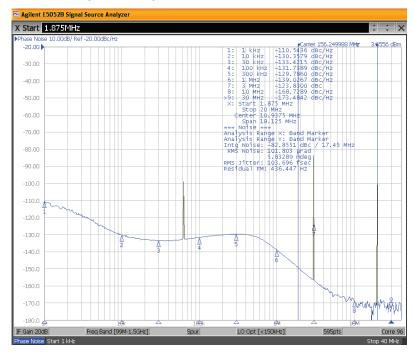

#### **□ JITTER ATTENUATION PERFORMANCE**

Example: 156.25MHz input test clock with bad phase jitter caused by a 3MHz spur - 1.1ps<sub>RMS</sub> of phase jitter for 1.875MHz to 20MHz integration range

Output Clock from ABMJB-903: The 3MHz spur is attenuated by 20dB, resulting in a phase jitter reduction from 1.1ps to 0.10ps for 1.875MHz to 20MHz integration range

ABMJB-903

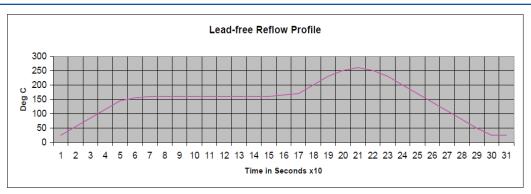

#### **REFLOW PROFILE:**

| Parameters                | Specifications     |

|---------------------------|--------------------|

| Average Ramp-up Rate      | 3°C /second max.   |

| Pre-Heat Temp 150 – 200°C | 60 – 180 second    |

| Temp > 217°C              | 60 – 150 second    |

| Time @ Peak Temperature   | 20 – 40 second     |

| Peak Temperature          | 260°C + 0°C / -5°C |

| Ramp-down Rate            | -6°C / second max. |

| Time 25°C to Peak Temp.   | 8 minutes max.     |

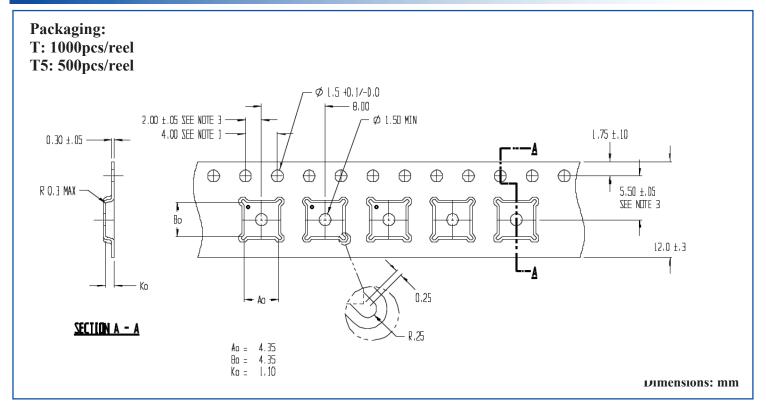

### **► TAPE & REEL:**

**ATTENTION:** Abracon Corporation's products are COTS – Commercial-Off-The-Shelf products; suitable for Commercial, Industrial and, where designated, Automotive Applications. Abracon's products are not specifically designed for Military, Aviation, Aerospace, Life-dependant Medical applications or any application requiring high reliability where component failure could result in loss of life and/or property. For applications requiring high reliability and/or presenting an extreme operating environment, written consent and authorization from Abracon Corporation is required. Please contact Abracon Corporation for more information.